# "Bulldozer"とAMD CPUの行方

# 増田 竜也 伊藤 博高

Tatsuya MASUDA Hirotaka ITO

## 1 はじめに

世界的な CPU のシェアは ,何年もの間 ,Intel と AMD の 2 社が占めている . 特に近年は , AMD のシェアが拡大の傾向にある  $^{1)}$  .

現在の CPU は、マルチコアが主体になっており、CPU 自体の処理能力を上げるのでなく、CPU の無駄を省き、効率化を図っている.そのため、AMD では、新しいアーキテクチャ「Bulldozer」を開発している.

## 2 AMD CPU

# 2.1 アーキテクチャ

AMD とは,アメリカの半導体製造会社であり,1969年に設立され,設立者は Dirk Meyer (ダーク・マイヤー)である  $^{2)}$  . AMD は,現在 K10 と呼ばれる CPU アーキテクチャをもとに,Phenom や Atlon などの CPU を製造している.K10 は,AMD64 と呼ばれる x86 アーキテクチャを AMD が拡張し,64 ビット化した命令セットによる設計により作られている.

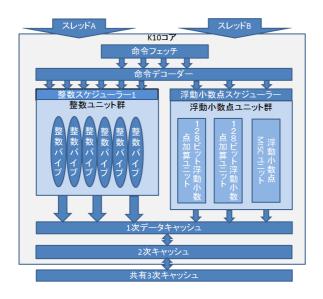

K10 のアーキテクチャを Fig.1 に示した.

Fig.1 AMD K10(参考文献 <sup>3)</sup> より参照)

整数スケジューラーの中の整数ユニット群に 6 つの整数パイプがあり,整数スケジューラーは 1 つになっている.基本的な処理の流れを以下に示す.

- 命令フェッチにより,スレッド A か,スレッド B を 読み取る.

- 2. 読み取ったコードを 6 命令デコーダで, スレッド内 の命令を細分化する.

- 3. その命令を整数スケジューラに送り,浮動小数点演算命令の場合は,浮動小数点ユニットに送る. スケジューラにて,最適な命令の処理の順番を決め,整数パイプにて処理する.

- 4. 浮動小数点ユニットによって行った処理も,整数ユニットで行った処理も1次データキャッシュに送る.

- 5.1 次データキャッシュから 2 次キャッシュに送り, 共有 3 次キャッシュに送り処理を完了する.

K10 は,従来の型より,整数パイプが 2 つから 3 つに増設され,内部命令である  $microOP(\mu OP)$  が  $6\mu OPs/Cycle$  の帯域となっていることで整数オペレーションのピークパフォーマンスが高くなっている.microOP とは,大きな命令の塊を,分解し,小さな命令になったものを指す.それにより,整数パイプで処理できるようになる 4 .

# 2.2 特徴

現在の CPU は , マルチコア化することで , 処理も早くなり , 3 次キャッシュも搭載されている . プロセッサを小さくし , コアを結合することで , クロックごとの性能が低く , オーバークロック耐性も低くなっている .

また,AMD 独自の構造として,メモリーコントローラと呼ばれる,コンピュータ上でRAMのデータの読み出しや書き出し,DRAMメモリのリフレッシュなどのメモリのインタフェースを統括する機能が,チップに内臓してある.これにより,メモリ待ち時間を短縮することでパフォーマンスを向上させている.

# 2.3 問題点

現在の PC 向け CPU は、3 つの命令の中から同時に実行可能な組み合わせを見つけて、命令の順序を並び替えて実行するアウトオブオーダーで実行している。しかし、命令同士に依存性があり、命令 1 で演算した値を命令 2 で使用する場合、二つの命令を並列に実行することはできない。そのため、多くの命令を並列に実行できるように並べ替えることは難しい。通常は x86 で 2 命令分程度までしか並列実行できない場合が多く、CPU の設計をマルチコアに適したものにする必要がある。そこで AMD

は,マルチコアに適した CPU アーキテクチャを開発し はじめた.

### 2.4 方向性

AMD は、CPU コアの効率を高めるため、CPU のダイ面積、つまり半導体チップの面積が、同時期の Intel CPU と比較して少し大きいものにしようとしている。そのため、ダイ面積あたりの、または消費電力当たりのパフォーマンスは低いものとなる。

具体的には , 整数コアを ,  ${

m Fig.1}$  にあるように現在の  ${

m K10}$  系の  ${

m 1}$  つから , 整数コアを  ${

m 2}$  つに変更する . そうすることで , 性能の効率は上昇する .

よって, AMD は少し CPU の性能は落ちるが, ピーク性能を追い求めるのをやめ, 性能の効率を求める方向性といえる.

## 3 次世代 CPU アーキテクチャ Bulldozer

### 3.1 Bulldozer とは

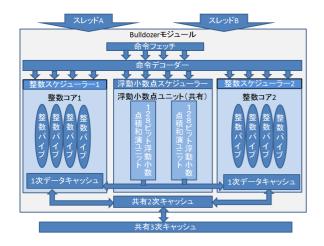

2009 年 11 月 11 日 ,2009 Financial Analyst Day にて , 次世代 CPU アーキテクチャとなる「Bulldozer」が発表された . その公開された Bulldozer のアーキテクチャを Fig.2 に示した . 2.1 節で述べた Fig.1 の  $6\mu$ OPs/Cycle である構造から , Fig.2 の  $4\mu$ OPs/Cycle で整数コアが 2 つの構造に変更されている .

Fig.2 Bulldozer(参考文献<sup>3)</sup> より参照)

## 3.2 特徴

6 命令デコーダから、4 命令デコーダに性能を落としているように見えるが、整数コアを 2 つにすることで効率化を図り、リソース同士の競合を防ぐため、1 次データキャッシュを、各整数コアに内臓している.また、浮動小数点演算ユニットの共有を実現し、さらなる性能の効率を上げている.

こういった設計は, $\mathrm{CPU}$  の方向性を根底から変えるものである. $\mathrm{Bulldozer}$  は,4 つのモジュールから構成されている. 2 個の  $\mathrm{CPU}$  コアを融合させたモジュールを基本単位として,1 つのモジュールの中に 2 つの整数コアを備え,2 スレッドを並列実行する仕様になっている.それぞれの整数コアは  $4\mu\mathrm{OPs}/\mathrm{Cycle}$  の帯域になっている.

これは , 現在 AMD に存在にする K10 系の整数ユニット郡の  $6\mu OP/Cycle$  の帯域より少ない . つまり , Bulldozerの整数パイプ群で実行できる命令のピーク実行帯域は , 現在の CPU の 2/3 になる . その分 , 整数オペレーションのピークパフォーマンスが低くなる .

### 3.3 内部構造

### 3.3.1 浮動小数点演算ユニット

浮動小数点演算ユニットとは, CPU が浮動小数点演算命令を実行するための回路である. Bulldozer の場合, Fig.2 にある浮動小数点スケジューラーの内部を指す.通常のプログラムでは, 浮動小数点演算命令が非常に少ない. そのため, 演算ユニットは空いたままになる.

AMD はワークロードの研究結果として,「すべてのアプリケーションのワークロードの中でもっとも使われている部分は整数演算ユニットであって,浮動小数点演算ユニットではない」と述べている  $^{3)}$  . そして,浮動小数点演算ユニットは  $\mathrm{CPU}$  の中でも,かなりの面積を占める.

今回の Bulldozer では、スレッドごとに備えるのではなく、スレッド間で共有にすることで効率的にしている。ところが、アプリケーションによっては、浮動小数点命令ばかりが多用される場合もある。この場合、浮動小数点の性能が低いと、アプリケーションの処理が目立ち、性能が低く感じられてしまう。

この点に関しても, $\operatorname{Bulldozer}$  は,演算自体の強化もしている.演算ユニットは2つで, $\operatorname{K10}$  コア時代と同じだが,それぞれのユニットが積和算を実行できる.積和算命令が実行できると,1つの命令で2つの演算を行うことができる.1 クロックに実行できる演算は,浮動小数点ユニットでは,現在の $\operatorname{K10}$  コアの2 倍の性能を発揮することを示している.

# 3.3.2 整数演算クラスタ

AMD は,Hyper-Threading のような Simultaneous Multithreading(以下 SMT) 技術では,整数演算リソースが十分でないと,リソースの競合が発生して性能が抑えられる問題がある.SMT とは,単一 CPU により複数の実行スレッドを同時に実行するプロセッサの機能を指す.

このため、2つの完全に別れた整数演算サブユニットを備え、1つの整数コアが他の整数コアと実行時に干渉することを防いだ、また、分離されたデータキャッシュ、分離されたスケジュールを備えている、このため、両方の整数演算コアが同時に実行される場合でも、シングルスレッドパフォーマンスは高いまま、維持できる.

一方,反対の意見も現れている.今後は,スループット重視のワークロードでは,浮動小数点演算をヘビーに使うアプリケーションが急増する傾向にあると指摘されている.このビジョンについては,AMD も Intel も同じように掲げている.AMD については,時間とともに,Bulldozer コアは APU と呼ばれる,AMD が開発している CPU に GPU を統合した新しいプロセッサにも使われると述べられている  $^{5)}$ .

また, APU SOC(System-on-a-chip) として非常に強力なデータ並列エンジンを CPU 上に備えることを考えている. SOC とは,1つの半導体チップ上に必要とされる一連の機能(またはシステム)を集積する集積手法の一つであるが,APUには,小さな浮動小数点演算ユニットの機能や GPU のデータ並列の浮動小数点演算機能などが乗ることが予想される.

### 3.4 マルチスレッティングの比較

デュアルコア,Hyper-Threading,Bulldozer の違いは,マルチスレッド実行による CPU のリソースをどのくらい共有するかの違いである.2 スレッドそれぞれ独立しているのがデュアルコアであり,ほとんど共有するのが Hyper-Threading である.そして Bulldozer は一部のリソースは共有するが,よく使うリソースはスレッドごと持つようになっている.つまり,Bulldozer はデュアルコアと Hyper-Threading の中間にあたる利点を持つ.その比較を Fig.3 に示した.Fig.3 の左に方式と技術を記載し,リソースのイメージ,それによるパフォーマンスの変化を順にを示した.デュアルコアのスループットとコストを基準に比較した.リソースを一部共有すれば,スループットは低下してしまうが,コストも減り,その中間である Bulldozer は効率的であることを示している.

| コア              | 処理の仕方                                                 | 性能     |

|-----------------|-------------------------------------------------------|--------|

| デュアルコア          | スレッド A スレッドBの専用リソース 専用リソース                            | スループット |

| Bulldozer       | スレッド A スレッド B スレッド B の専用リ Bの共有リ ソース ソース ソース           | スループット |

| Hyper-Threading | スレッドA<br>スレッドAの専用<br>リソース スレッドAとB<br>の共有リ<br>ソース リソース | スループット |

Fig.3 マルチスレッディングの比較 (参考文献<sup>3)</sup> より 参照)

デュアルコアより効率的に実行スレッドを増やしているパフォーマンス向けの CPU は現在, $45\mathrm{nm}$  プロセスでクアッドコアまで, $32\mathrm{nm}$  プロセスでも 6 コア載せるのが限界であった.しかし,Bulldozer の場合,同じ  $32\mathrm{nm}$  プロセスの CPU に 4 つのモジュール,8 つのコアを載せることが可能である.2011 年には,恐らく 1 万円台後半で 8 コア/8 スレッドである Bulldozer が,購入できるようになる.その結果,同じ価格で発揮できる性能の 1.8 倍のマルチスレッド性能が得られると予想される.

# 4 まとめ

現在,Bullzoer について発表されていることは,2 つのスレッドを同時実行できるが,SMT と異なり,整数実行ユニットはスレッド間で共用されない.整数演算は 4

命令のアウトオブオーダーであり,2 ロード/サイクルをスレッドごとに実現することができる.

また CPU のリソースを一部共有することで,デュアルコアより効率的に実行スレッドを増やすことができる.結果として,CPU の性能は下がってしまうが,それに引き換え,CPU の無駄を省き,効率化を特化したものとなる.

## 5 今後の展望

2009 Financial Analyst Day にて ,AMD CPU の 2010 から 2011 年のロードマップが公開された . AMD 初のモバイル用のクアッドコアを搭載したノート PC のプラットフォームの開発や , DirectX11 グラフィックスへの対応などを視野にしている . 特に注目すべきものは , 2011 年に登場する「Fusion」と呼ばれる , CPU+GPU が 1 枚のダイ面積で提供される . CPU 側に GPU を内臓することで , 性能を格段に上げることを図っているが , プラットフォームの変更が生じると言われている 6 .

残念なことに,今回 AMD が発表した Bulldozer の性能は,同時期の Intel の CPU の性能を上回るものではなかった.Intel CPU の場合,同じ 32nm プロセスで 6 コアに加え,Hyper-Threading で 12 スレッド実行可能である.やはり,技術面で Intel に一歩後退しているのが現状である.しかし,先行されるが,追いついていっている.Hyper-Threading の欠点でもある,同じ CPU コアを共有する 2 つのスレッドがリソースを取り合い,結果的に性能が落ちてしまう可能性もある.

今まで,整数パイプの幅は,広げる傾向にあり,今回の AMD の決断は,かなりのリスクを負うものである.時代に合わせたアーキテクチャを提供しなければ,せっかくの新技術も生かすことができない.

私の意見としては,これから数年は,コアを増やし続ける傾向は続き,それに合わしたアーキテクチャを提供する形になると思う.ただ,コアの数による性能アップを狙う一方,ほかの視点からの展開も必要となるだろう.とくに AMD が開発中の CPU と GPU を結合する APUは,モバイル PC において,基盤の面積の占有率を下げたり,それによる電力消費の削減が見込まれる.大量の計算量を必要とする,3D グラフィックや HPC において,こういった CPU と GPU の新しいアーキテクチャの形により,活躍が期待できるといえる.

### 参考文献

- 1) Fudzilla. http://www.fudzilla.com/.

- 2) Amd. http://www.amd.com/jp-ja/.

- 3) Pc watch. http://pc.watch.impress.co.jp/.

- 4) 坪山博貴. CPU の謎. ソーテック社, 2005.

- 5) Pc online. http://pc.nikkeibp.co.jp/.

- 6) アスキーデジタル. http://www.ascii.jp/digital/.