# メモリの行方

#### Memory of Next Generation

## 羽山 徹彩, 近藤 健史

Tessai Hayama, Takefumi Kondo

**Abstract:** In this paper,we introduced memories of next generation. They are three kinds; VM-CSDRAM, DRDRAM and DDRSDRAM. We thougt and chosed which memory will be main stream, refering to market research and their architecture.

## 1 はじめに

メモリは、CPUや FSB(Front Side Bas) と共にコンピュータの高速性に欠かせない要素の一つである。CPUの急激なクロックの向上により、パソコンの動作速度は速くなっている。しかしながら、CPUだけが速くなっても、その動作に必要なシステムバスやメモリの動作が向上しなければ総合的な動作の向上は望めない。

このような背景から,近年,メモリの急激な性能の向上が始まっている。今回の発表では,VCMSDRAM,DDRSDRAM,DRDRAMという高速な次世代メモリの規格を示し,そして,その技術的側面と市場動向にふれながら,主流になるであろうメモリについて考察する.

#### 2 メモリの仕組み

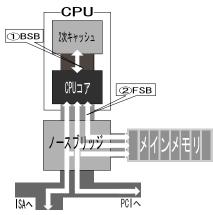

メモリの動作の仕組みとして大切であると思われるバス幅について fig.1 をもとに以下に示す.

${

m BSB(Back\ Side\ Bas)}$  は,2 次キャッシュへの専用のバスで,高速の 2 次キャッシュへのアクセスを可能にしている.

FSB は , メモリや PCI バスなどと ノースブリッジ を経由して接続するバスである . この FSB のバス幅を 大きくすることで , 高速のメモリのアクセスが実現する .

現在,2 次キャッシュの BSB のクロックは,CPU のコアクロックと同じになるだけの技術がある.ただし,FSB は現在主流の PC100SDRAM が 100MHz である.そのため,CPU が 500MHz で動作している場合は,その 5 分の 1 でしかデータのやり取りができないことになる.これよりメモリの課題は,メモリのバス幅×動作クロックを CPU コアクロックと同程度に持っていくことである.

# 3 メモリの歴史

## 3.1 SRAM

SRAM は 2 次キャッシュで用いる.Intel486 時代 (1989年ごろ) に主流であったのが SRAM(StaticRAM) であり, バスクロックよりも低速で動作する.

Fig. 1 メモリの環境

B-SRAM(Burst-SRAM) が,1回のアドレス指定によって連続データへのアクセスを可能とした。これは,Pentium 初期のマザーボードに搭載されていた.

そして, C-SRAM(Custum-SRAM) は, Pentium Xeon, pentium Xeon などの CPU パッケージ内部にとりこまれている高速な SRAM で, コアクロックとの同期を完全にとってのアクセスができる. このことより SRAM の進化は, 落ち着いたと考えられる<sup>3)</sup>.

#### **3.2** DRAM

次に, $\mathrm{DRAM}$  における過去のメモリを古いものから順に示す.

## 1. FPDRAM(Fast Page DRAM)

DRAM からの読み込み時に行アドレスを指定すると、その行のすべてのデータが行バッファに読み出される. これより、同一行の読み出しに列アドレスのみを指定するだけで、データの読み込みが可能. Intel486 時代に主流であった.

#### 2. EDODRAM(Extend Date Out DRAM)

CPU が読み込みを指定する際に行う, 行アドレスの指定と, これに対するデータの読み出しを同時に行うことが可能. 1995 年から Pentium 用として用いられた.

3. SDRAM(Synchronous DRAM)

メモリ自体がマザーボード上のバスクロックに同期 し、このタイミングでのデータの転送が可能であ る、1998年以降主流となった.

以上のように, さまざまなアルゴリズムを用いることにより, より速いデータ転送速度を実現させてきた $^{1}$ ).

### 4 次世代メモリの技術

## 4.1 次世代のメモリの種類

現在の主流は PC100SDRAM であるが,より高速な次世代メモリの4つの規格について以下に示す.

#### • VCMSDRAM

VCM は , ページのヒット率を上げてメモリの実行 効率を上げる技術である . メモリコアと I/O インターフェイスの間にチャンネルという一種のキャッシュを搭載する . 技術的にはどの DRAM にも搭載できるが , VCM のチャンネルにはメモリコントローラ側に高いインテリジェンスが必要とされる .

#### • DRDRAM(Direct Rambus DRAM)

PC800DRDRAM では,バスクロックを $800 \mathrm{MHz}$ ,バス幅を16 ビットに拡張することによって,最大 $1.6 \mathrm{GB/s}$  の転送速度を実現する.最高 $800 \mathrm{MHz}$  という高速サイクルで小分けにしたデータを転送する.ただし,現在はこれをサポートしているメモリチップは $\mathrm{Intel} 820$  のみである.

• DDRSDRAM(Duoble Date Rate SDRAM)

${

m SDRAM}$  のクロックのエッジの両端を使う技術で,データ転送だけを 2 倍のクロックで行う. つまり, ${

m PC}266$  の場合は,ベースが  $133{

m MHz}$  でデータ転送は  $266{

m MHz}$  になる.

# **4.2** DRDRAM と SDRAM のメモリアーキテクチャの比較

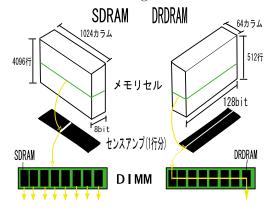

SDRAM と DRDRAM の違いは,メモリセルに蓄積された情報をどのようにメモリバスに送り出すかである.メモリセルは,8bit単位で縦横のメッシュ上に並べられており,CPU がどの行どの列の情報を取り出すかを指定することで特定のメモリセルを指定する.これにより,特定の場所にある情報のみを取り出している.このための回路をセンスアンプという.

SDRAM は , 1 行分のデータを一気に転送している . しかし , センスアンプに複写された 1 行分のデータから , 8bit ×数列分を一度に出力することはできない . そこでこの中から特定の 1 列を指定して 8bit 分だけ読み出す . SDRAM は , この出力信号が対応する周波数クロックに同期するため , サイクル速度で 8bit ずつ出力される . 64bitDRDRAM の場合 , メモリセルは , 128bit 単位で並べられている . このため , 最終的に読み出したデータ

は 128bit と SDRAM の 16 倍に相当する情報を読み出すことができる. ただし, このまま出力したのでは, データ出力用に 128 もの信号線が必要になってしまう. そこで, 128bit のデータを 16bit 単位に分解して転送するようにしている. 読み出した 128bit のデータは転送用のバッファに収められているので, 非常に高速に送信することができる<sup>2)</sup>. 概要は Fig.2 に示す.

Fig. 2 SDRAM と DRDRAM の技術比較

#### 5 メモリの市場

VCMSDRAM は,NECの特許であるため,著作権にかかわるコストに対するメリットが合うかどうかが問題である.

DRDRAM は唯一対応しているチップセット Intel820 の出荷が遅れたことで DRDRAM に対応する製品の製造を遅らした。また , 対応している製品がほとんど存在していないため , 当初は量産効果も期待できない .

DDRDRAM の生産ラインは SDRAM の生産ライン とはほとんど変わらず , SDRAM の 103 %のコストで 生成可能である $^{1)}$  .

#### 6 まとめ

メモリの技術と市場を考慮して,将来的には DR-DRAM が主流になると考えられる.その理由として,4.2 で記述したように,アーキテクチャ的に DRDRAM の方が SDRAM よりも画期的である.しかし,市場的に DRDRAM の価格がマスプロダクションにより落ちるのはまだ先であると考えられる.そのため,早期に DR-DRAM が主流になることは考えにくい. 以上から,メモリの移り変わりとして PC133SDRAM から VMCを用いた PC133SDRAM,そして,DDRSDRAM,DRDRAMと移行していくと考えられる.

#### 参考文献

- 1) 『DOS/V POWER』(インプレス,1999年/9月号)

- 2) 『ASC 』(アスキー社,1999年/11月号)

- 3) 小泉修『PC アーキテクチャの全て』(日本実業出版 社,2000年)