# 次世代 CPU の行方

The future of the next generation's CPU

## 有賀浩,吉田純一

Hiroshi ARUGA, Jun-ichi YOSHIDA

**Abstract:** This paper introduces some technologies for high performance CPU and the trend of next generation CPU. There is various ways to enhance the performance of CPU. Among of these technologies, EPIC and VLIW architecture are picked up. And more, Intel Architecture 64(IA-64) and Crusoe processor are given as the concrete example of these technologies.

## 1 はじめに

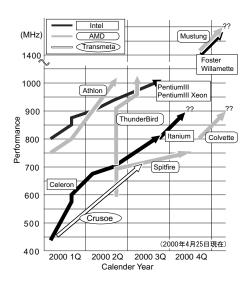

現在 Intel, AMD 両社が 1GHz の CPU をめぐり技術力を競い合っている. Intel 側は Pentium の後継にあたる「Willamette」, Pentium Xeon の後継の64bitCPUである「Itanium」(後述), Celeron の後継である「Timna」などを発表している. それに対して AMD側はコアに 2 次キャッシュを統合した「Thunderbird」と「Spitfire」, 更には 2001 年投入目標の 64bitCPU「SledgeHammer」などを発表している.

ここでは 64bitCPU などの次世代 CPU のあり方とその技術について,具体的な例を取り上げて考察する.

Fig. 1 CPU ロードマップ <sup>1, 2)</sup>

## 2 64bit へ移行する理由<sup>5)</sup>

64bit へ移行する最大の理由は管理できるメモリ空間を拡張することである.現在の 32bitCPU では 4GB までメモリを管理することが可能であり,現時点では大抵のアプリケーションはこの容量で扱うことができる.ところが,最近の大規模データベースなどではアプリケーションサイズが巨大化し,4GB 以上のメモリが必要とな

るケースも増えている.これらの大規模アプリケーションでは  $32 {

m bit CPU}$  はメモリ空間を管理することは不可能である.また  $4 {

m GB}$  以下のものでも,メモリヘアクセスしてデータを読み込むのに通常よりも長い時間が必要とり,パフォーマンスが低下してしまう.

このような大規模なメモリ空間を管理し、高速アクセスを実現するためには CPU のバス幅 (bit 数) を増やせばよいが、単に 64bit 化しただけではその性能を発揮することができない。64bit CPU の性能を十分に発揮するためのアーキテクチャとして、Intel は「Intel Architecture (IA) 64」の開発に全力を注いでいる。

## 3 CPU の高速化技術

## 3.1 明示的な並列化 (EPIC)<sup>6)</sup>

64bit のマイクロプロセッサはより多くの並列実行を 行うため、性能向上の妨げとなる分岐命令やプロセッサ とメモリ間の遅延、現在の逐次型プログラミング・モデ ルがより重要な問題となる.EPIC(Explicitly Parallel Instruction Computer) 技術とは、明らかに並列化した 方がよいと分かる部分についてはソフトウェアが CPU に明示的に働きかけるようなプログラミングを可能にす る技術である.現在のプロセッサ・アーキテクチャを用 いた場合、逐次処理に関わる問題が存在するが、EPIC 技術では分岐数や分岐予測ミス、メモリとプロセッサ間 の遅延を減少し性能向上を図ることができる.

IA-64ではこの EPIC 技術により高性能化とコンピューティングの進展を実現している. なお IA-64 プロセッサは, IA-32 ベースのソフトウェアおよびオペレーティングシステムとの完全互換性を維持し, ハイエンドのサーバやワークステーションに必要な性能と機能を提供することができる. Fig1 に示した CPU の中で 64bit のものは Itanium である.

#### 3.2 VLIW(Very Long Instruction Word)<sup>3, 4)</sup>

現在の RISC アーキテクチャのプロセッサでは回路自体が非常に大規模で複雑になりすぎてしまうという問題

がある.x86<sup>1</sup> 系の命令セットが並列処理に適さないため,RISC ライクな命令に変換したり,命令の順序を最適化するなどの複雑な処理を行い,処理性能を高めている.現在の CPU はこれらの処理をハードウェアで実現するため,回路が大規模で複雑になり,結果的にコストが高くなってしまう.

この問題はVLIW アーキテクチャを用い,x86命令をソフトウェア的に変換することで解決することが可能である.ハードウェア的に変換し最適化する方法では上述の通りコストや消費電力の問題が生じるが,ソフトウェアにより命令変換をすれば回路を複雑にする必要がないため,回路の規模を大幅に削減することができ,消費電力を非常に低く抑えることが可能となる.これまでのように単純で短い命令を複数集めたRISC アーキテクチャとは逆に,VLIW アーキテクチャでは複数の機能を持たせた非常に長い命令セットを用いる2.その上で予め効率のよい処理方法をプログラムし,並列度を向上させるのである.

## 3.2.1 VLIW アーキテクチャを採用した $CPU^{3, 4}$

VLIW アーキテクチャを用いて並列化し,高速化を図った CPU の一つとして Transmeta 社の Crusoe がある. Crusoe はシンプルな構造のハードと高度なエミュレーション技術により x86 互換を実現する CPU である. ハードがシンプルである分コストを抑え,消費電力が少ない分モバイル端末で使用すればバッテリーを現在の3倍以上にすることが可能になる.

Crusoe では x86 命令をすべて実行するために, Code Morphing Software (CMS) と呼ばれるソフトウェアとともに動作し, CMS 内で x86 命令を VLIW 命令に変換するエミュレーションを行っている.また,プロセッサに 2MB の翻訳バッファを持たせ,いったん VLIW 命令に変換した命令コードをキャッシュすることで性能を高めている.

Crusoe は 32bit のコードを 4 個パックにした 128bit の VLIW を採用している.このため同時に実行できる機能をあらかじめ 1 命令としてプログラムすることで並列度を向上させ,処理速度を高めることができる.

Crusoe は, Intel などが目指しているハイエンドの CPU とは別の角度から高速化を図った,モバイル端末に最適な省電力設計の高性能 CPU と言える.

## **3.2.2** Crusoe の弱点 <sup>4)</sup>

前述の通り、Crusoe の性能はソフトウェア (CMS) に依存するところが大きい、Crusoe では複雑で大規模なアプリケーションを実行した場合、CMS による命令の変換が何度も行われ、パフォーマンスが低下するという問

Fig. 2 Transmeta  $\mathcal{O}$  Crusoe(TM3120)

題が指摘されている.しかしこの問題はエミュレーション技術の発達に伴い解決することができるが,その技術進歩が遅ければ CPU の持つポテンシャルを使い切ることができないと言える.

#### 4 おわりに

最近の CPU 業界の動向は激しく、高性能の新モデルが続々と発表されている.また Fig1 を信じるならば、来年の今ごろには 1.4GHz 程度の CPU や、IA-64 系の CPU が数多く登場しているはずである.しかしこれらの CPU のほとんどはサーバーやワークステーション向けでコストが高いため、一般市場に出回るにはまだ時間がかかりそうである.

それに対し,コストの割に高パフォーマンスの ThunderBird やその廉価版である Spitfire がそれぞれハイエンド,ローエンド市場において,一般向けデスクトップ用 CPU として人気を集めると予想され, Intel のハイ,ローエンド向けの高性能 CPU の開発が待たれるところである.

またモバイルに関しては、Transmeta が主要パソコンメーカーのソニー、Compaq、Gateway など 9 社から総額 8,800 万ドルの出資を受けるなどのホットな話題もあり、4 月 24 日にモバイル用の PentiumIII と Celeron を発表した Intel や他の企業との間で今以上に激しい競争が行われそうである.

## 参考文献

- 1) 川上 真 CPU **バイヤーズガイド**~2000 年春 『日経 WinPC 4月号』(日経 BP 社, 2000)

- 2) 川上 真 最新 CPU & マザーボード徹底攻略『日経 WinPC 5月号』(日経 BP 社, 2000)

- 3) 本田 雅一 特集 最新 CPU 新聞 『月刊 ASCII 2 月号』(株式会社アスキー, 2000)

- 4) 本田 雅一 教えて! Crusoe『月刊アスキー 3月号』(株式会社アスキー,2000)

- 5) FInside Intel's Merced: A Stragegic Planning Discussion A http://www.aberdeen.com

- 6) 『次世代型 64 ビット命令セット・アーキテクチャ初公開』 http://www.intel.co.jp/jp/intel/pr/press/jointhp.htm

$<sup>^1</sup>$ Intel の 16bitCPU「8086」に始まり,Pentium / へ受け継がれてきたマイクロコードアーキテクチャ.

<sup>&</sup>lt;sup>2</sup>ロード・ストアなど複数の命令を 1 つの長い命令語の中に収める